Tasarımıfotonikentegre devre

Fotonik entegre devreler(PIC'ler), interferometrelerde veya yol uzunluğuna duyarlı diğer uygulamalarda yol uzunluğunun önemi nedeniyle genellikle matematiksel komut dosyaları yardımıyla tasarlanır.RESİMFoto maske, genellikle GDSII formatında temsil edilen birçok çokgen şekilden oluşan, bir wafer üzerine çok sayıda katman (tipik olarak 10 ila 30) desenlenerek üretilir. Dosyayı fotomask üreticisine göndermeden önce, tasarımın doğruluğunu doğrulamak için PIC'i simüle edebilmek son derece önemlidir. Simülasyon birden fazla seviyeye ayrılır: en düşük seviye, simülasyonun alt dalga boyu seviyesinde gerçekleştirildiği üç boyutlu elektromanyetik (EM) simülasyondur; ancak malzemedeki atomlar arasındaki etkileşimler makroskobik ölçekte ele alınır. Tipik yöntemler arasında üç boyutlu sonlu fark zaman alanı (3D FDTD) ve özmod genişletme (EME) bulunur. Bu yöntemler en doğru olanlardır, ancak tüm PIC simülasyon süresi için pratik değildirler. Bir sonraki seviye, sonlu fark ışın yayılımı (FD-BPM) gibi 2,5 boyutlu EM simülasyonudur. Bu yöntemler çok daha hızlıdır, ancak doğruluktan ödün verirler ve yalnızca paraksiyel yayılımı ele alabilirler ve örneğin rezonatörleri simüle etmek için kullanılamazlar. Bir sonraki seviye, 2D FDTD ve 2D BPM gibi 2D EM simülasyonudur. Bunlar da daha hızlıdır, ancak polarizasyon döndürücülerini simüle edememeleri gibi sınırlı işlevselliğe sahiptirler. Daha ileri bir seviye ise iletim ve/veya saçılma matrisi simülasyonudur. Her ana bileşen, giriş ve çıkışa sahip bir bileşene indirgenir ve bağlı dalga kılavuzu bir faz kayması ve zayıflama elemanına indirgenir. Bu simülasyonlar son derece hızlıdır. Çıkış sinyali, iletim matrisinin giriş sinyaliyle çarpılmasıyla elde edilir. Saçılma matrisi (elemanlarına S-parametreleri denir), bileşenin diğer tarafındaki giriş ve çıkış sinyallerini bulmak için bir taraftaki giriş ve çıkış sinyallerini çarpar. Temel olarak, saçılma matrisi eleman içindeki yansımayı içerir. Saçılma matrisi genellikle her boyutta iletim matrisinin iki katı büyüklüğündedir. Özetle, 3D EM'den iletim/saçılım matrisi simülasyonuna kadar her simülasyon katmanı hız ve doğruluk arasında bir denge sunar ve tasarımcılar tasarım doğrulama sürecini optimize etmek için kendi özel ihtiyaçlarına uygun simülasyon seviyesini seçerler.

Ancak, belirli elemanların elektromanyetik simülasyonuna güvenmek ve tüm PIC'yi simüle etmek için bir saçılma/transfer matrisi kullanmak, akış plakasının önünde tamamen doğru bir tasarımı garanti etmez. Örneğin, yanlış hesaplanmış yol uzunlukları, yüksek dereceli modları etkili bir şekilde bastıramayan çok modlu dalga kılavuzları veya beklenmedik bağlantı sorunlarına yol açan birbirine çok yakın iki dalga kılavuzu, simülasyon sırasında tespit edilemeyebilir. Bu nedenle, gelişmiş simülasyon araçları güçlü tasarım doğrulama yetenekleri sağlasa da, tasarımın doğruluğunu ve güvenilirliğini sağlamak ve akış şemasının riskini azaltmak için tasarımcının yüksek derecede dikkat ve özenli incelemesi, pratik deneyim ve teknik bilgiyle birleştirilmesi gerekmektedir.

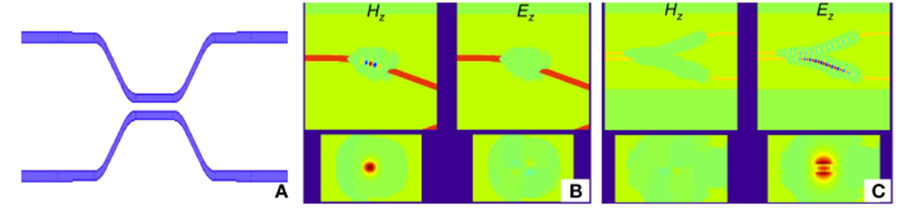

Seyrek FDTD adı verilen bir teknik, tasarımı doğrulamak için eksiksiz bir PIC tasarımı üzerinde doğrudan 3B ve 2B FDTD simülasyonlarının gerçekleştirilmesine olanak tanır. Herhangi bir elektromanyetik simülasyon aracının çok büyük ölçekli bir PIC'i simüle etmesi zor olsa da, seyrek FDTD oldukça geniş bir yerel alanı simüle edebilmektedir. Geleneksel 3B FDTD'de, simülasyon belirli bir nicelleştirilmiş hacim içindeki elektromanyetik alanın altı bileşenini başlatarak başlar. Zaman ilerledikçe, hacimdeki yeni alan bileşeni hesaplanır ve bu böyle devam eder. Her adım çok fazla hesaplama gerektirir, bu nedenle uzun zaman alır. Seyrek 3B FDTD'de, hacmin her noktasında her adımda hesaplama yapmak yerine, teorik olarak keyfi olarak büyük bir hacme karşılık gelebilecek ve yalnızca bu bileşenler için hesaplanacak bir alan bileşenleri listesi tutulur. Her zaman adımında, alan bileşenlerine bitişik noktalar eklenirken, belirli bir güç eşiğinin altındaki alan bileşenleri çıkarılır. Bazı yapılar için bu hesaplama, geleneksel 3B FDTD'den birkaç kat daha hızlı olabilir. Ancak, seyrek FDTD'ler dağılımlı yapılarla uğraşırken iyi performans göstermezler çünkü bu durumda zaman alanı çok fazla yayılır ve sonuç olarak çok uzun ve yönetilmesi zor listeler oluşur. Şekil 1, polarizasyon ışın ayırıcısına (PBS) benzer bir 3B FDTD simülasyonunun örnek bir ekran görüntüsünü göstermektedir.

Şekil 1: 3 boyutlu seyrek FDTD'den elde edilen simülasyon sonuçları. (A) Simüle edilen yapının, yani yönlü bir kuplörün üstten görünümüdür. (B) Yarı-TE uyarımı kullanılarak yapılan bir simülasyonun ekran görüntüsünü göstermektedir. Yukarıdaki iki diyagram, yarı-TE ve yarı-TM sinyallerinin üstten görünümünü, aşağıdaki iki diyagram ise karşılık gelen kesit görünümünü göstermektedir. (C) Yarı-TM uyarımı kullanılarak yapılan bir simülasyonun ekran görüntüsünü göstermektedir.

Yayın tarihi: 23 Temmuz 2024